Исследование иерархических технологий для проектирования систем на кристалле

В последние годы интеграция систем на кристалле (СнК) в архитектуры современных встроенных систем происходит повсеместно. Система на кристалле – это СБИС, объединяющая на одном чипе различные функциональные блоки, которые образуют законченное изделие для автономного применения в электронной аппаратуре [1].

СнК может состоять как из одного вычислительного узла, так и из большого числа IP-ядер и узлов периферии. Задачи, которые должны решаться с помощью СнК, становятся более сложными и трудоемкими, поэтому необходимо применять многопроцессорные СнК, в которых сетевые архитектуры в виде сетей на кристалле вытесняют решения, где вычислительные ядра соединены высокопроизводительными шинами [2]. Требуется поиск новых топологических решений, которые бы позволили организовать подсистему связи СтнК так, чтобы она удовлетворяла все возрастающим требованиям.

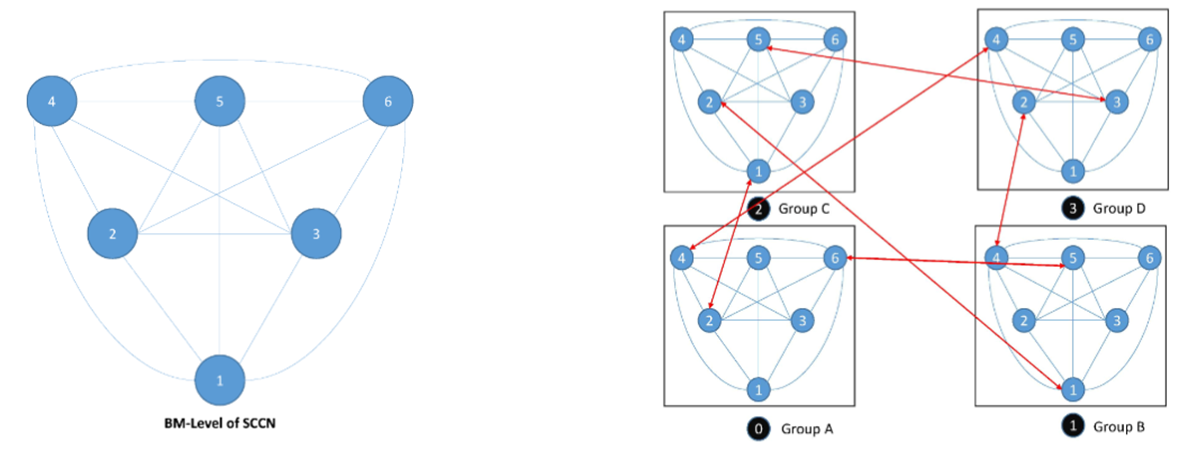

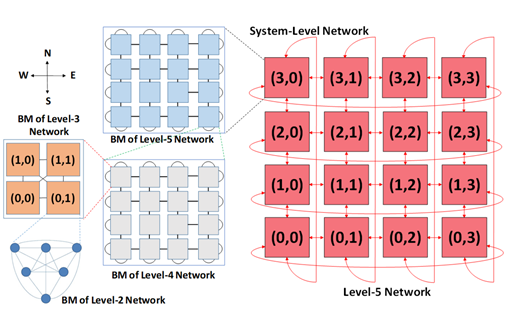

Данный проект заключается в проведении исследования подхода, используемого в работах Хафизура Рахмана [3], состоящего в построении новых топологий с использованием иерархического подхода. Необходимо реализовать алгоритм маршрутизации, предложенный Хафизуром Рахманом, с целью последующего аналитического анализа алгоритма и моделирования сетей на кристалле с новыми топологиями, а также поиска, как данный подход можно применить для комбинаций других топологий.

Новизна модифицируемого подхода состоит в замещении топологий разного уровня предложенной иерархической структуры циркулянтными графами, а также подклассом циркулянтных графов - графами Пэли.

Цель:

- разработка программного обеспечения для проведения исследования иерархических топологий сетей на кристалле;

- поиск новых топологий и комбинаций известных топологий для достижения лучших топологических параметров подсистемы связи в сетях на кристалле.

Исходные данные:

- Алгоритм маршрутизации, предложенный Хафизуром Рахманом;

- Проведенное исследование корневого и прямого произведений графов Пэли между собой и на кольцевые графы [4].

Ожидаемые результаты:

Программное обеспечение, принимающее на вход сигнатуру графа, помещаемый на нулевой уровень иерархической топологии, с последующей визуализацией и подсчетом основных характеристик получившейся графовой структуры.

Практическая часть проекта должна включать в себя инструмент визуализации и подсчета основных характеристик графов, а также результаты моделирования сетей на кристалле с новыми топологиями.

Используемые средства разработки:

Разработка программы ведется на следующих языка программирования и с использованием следующих программных средств:

- Python;

- Gephi;

- PCG Console.

Этапы:

- исследование подхода, используемого в работах Хафизура Рахмана, состоящего в построении новых топологий с использованием иерархического подхода;

- реализация алгоритма маршрутизации;

- аналитический анализ алгоритма и моделирование сетей на кристалле с новыми топологиями;

- поиск новых топологий и комбинаций известных топологий для достижения лучших топологических параметров подсистемы связи в сетях на кристалле.

Ограничения:

- максимальный размер сетки уровня сети – (4 x 4);

- максимальное кол-во уровней сети – 5;

- максимальное кол-во узлов 0-го уровня сети – 101.

Команда проекта:

Список использованных источников

1. И. Шагурин, “Системы на кристалле. Особенности реализации и перспективы применения”, Электронные компоненты, №1, 2009. С. 37–39.

2. K.K. Ryu, E. Shin, and V.J. Mooney, “A comparison of five different multiprocessor SoC bus architectures,” in Proceedings Euromicro Symposium on Digital Systems Design, 2001, pp. 202–209, doi: 10.1109/DSD.2001.952283.

3. M.M. Hafizur Rahman, M.N.M. Ali, A. A. Ibrahim, D.K. Behera, Y. Miura, and Y. Inoguchi, “A New Static Cost-Effective Parameter for Interconnection Networks of Massively Parallel Computer Systems,” in Advances in Intelligent Systems and Computing, vol. 758, Springer Verlag, 2019, pp. 147–155, doi: 10.1007/978-981-13-0514-6_15.

4. Rzaev E. R., Romanov A. The New Promising Network-on-Chip Topologies Development Using Product Operation, in: 2021 International Russian Automation Conference (RusAutoCon). IEEE, 2021. P. 421-425, doi: 10.1109/RusAutoCon52004.2021.9537317.

5. M.M. Hafizur Rahman, F. Al Faisal, R.M. Nor, T.M.T. Sembok, D.K. Behera, and Y. Inoguchi, “Cost Effectiveness Analysis of a Vertical Midimew-Connected Mesh Network (VMMN),” in Advances in Intelligent Systems and Computing, 2017, pp. 45–53, doi: 10.1007/978-981-10-3874-7_5.

Руководители проекта

Департамент компьютерной инженерии: Доцент

Нашли опечатку?

Выделите её, нажмите Ctrl+Enter и отправьте нам уведомление. Спасибо за участие!

Сервис предназначен только для отправки сообщений об орфографических и пунктуационных ошибках.