Exploring hierarchical technologies for system-on-a-chip design

In recent years, the integration of systems on a chip (SoC) into the architecture of modern embedded systems is happening everywhere. A system on a chip is a VLSI that combines various functional blocks on a single chip, which form a complete product for autonomous use in electronic equipment [1].

A SoC can consist of either a single computing node or a large number of IP cores and peripheral nodes. The tasks that should be solved with the help of SoCs are becoming more complex and time-consuming, so it is necessary to use multiprocessor SoCs, in which network architectures in the form of networks on a chip are replacing solutions where computing cores are connected by high-performance buses [2]. It is necessary to search for new topological solutions that would make it possible to organize the communication subsystem of STNK so that it meets the ever-increasing requirements.

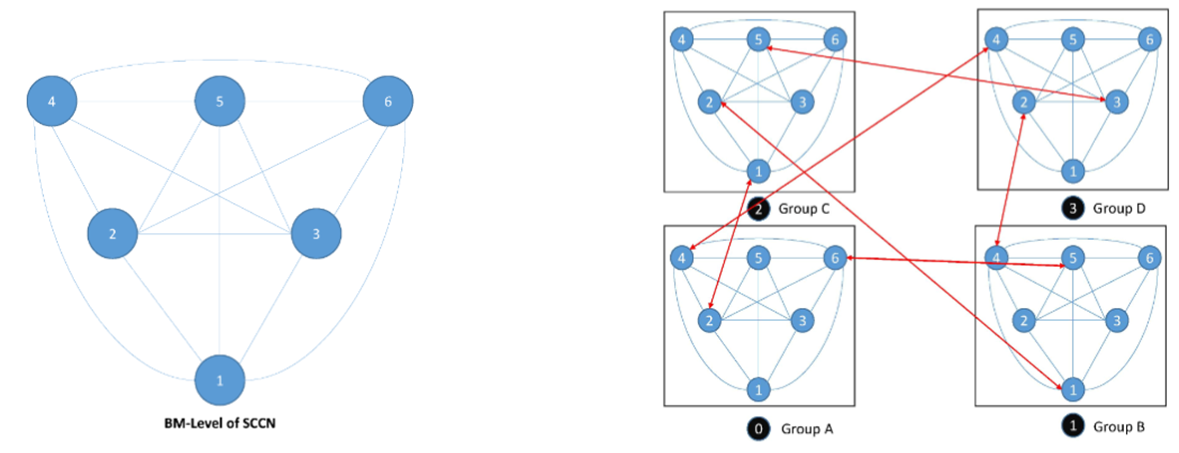

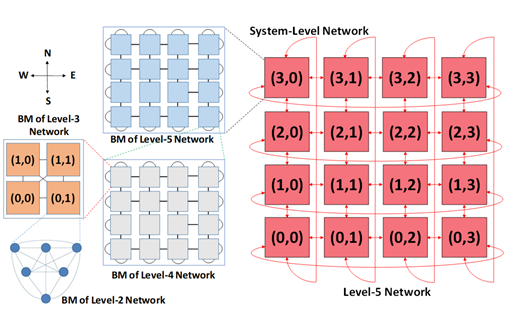

This project is to conduct a study of the approach used in the works of Hafizur Rahman [3], which consists in constructing new topologies using a hierarchical approach. It is necessary to implement the routing algorithm proposed by Hafizur Rahman with the aim of further analytical analysis of the algorithm and modeling of networks on a chip with new topologies, as well as finding how this approach can be applied to combinations of other topologies.

The novelty of the modified approach lies in the replacement of topologies of different levels of the proposed hierarchical structure with circulant graphs, as well as with a subclass of circulant graphs - Paley graphs.

Objective of the project:

- development of software for the study of hierarchical topologies of networks on a chip;

- search for new topologies and combinations of known topologies to achieve the best topological parameters of the communication subsystem in networks on a chip.

Initial data:

- Routing algorithm proposed by Hafizur Rahman;

- The study of the root and direct products of Paley graphs with each other and with ring graphs [4].

Expected results:

Software that accepts a graph signature as input, placed on the zero level of the hierarchical topology, with subsequent visualization and calculation of the main characteristics of the resulting graph structure.

The practical part of the project should include a tool for visualizing and calculating the main characteristics of graphs, as well as the results of modeling networks on a chip with new topologies.

Development tools used:

The program is developed in the following programming languages and using the following software tools:

- Python;

- Gephi;

- PCG Console.

Stages:

- study of the approach used in the works of Hafizur Rahman, which consists in constructing new topologies using a hierarchical approach;

- implementation of the routing algorithm;

- analytical analysis of the algorithm and modeling of networks on a chip with new topologies;

- search for new topologies and combinations of known topologies to achieve the best topological parameters of the communication subsystem in networks on a chip.

Restrictions:

- maximum network layer grid size - (4 x 4);

- maximum number of network levels - 5;

- the maximum number of nodes of the 0th level of the network is 101.

The project team:

List of sources used:

- References 1. I. Shagurin, “Systems on a crystal. Implementation features and application prospects”, Electronic Components, No. 1, 2009, pp. 37–39.

- K.K. Ryu, E. Shin, and V.J. Mooney, “A comparison of five different multiprocessor SoC bus architectures,” in Proceedings Euromicro Symposium on Digital Systems Design, 2001, pp. 202–209, doi: 10.1109/DSD.2001.952283.

- M.M. Hafizur Rahman, M.N.M. Ali, A.A. Ibrahim, D.K. Behera, Y. Miura, and Y. Inoguchi, “A New Static Cost-Effective Parameter for Interconnection Networks of Massively Parallel Computer Systems,” in Advances in Intelligent Systems and Computing, vol. 758, Springer Verlag, 2019, pp. 147–155, doi: 10.1007/978-981-13-0514-6_15.

- Rzaev E. R., Romanov A. The New Promising Network-on-Chip Topologies Development Using Product Operation, in: 2021 International Russian Automation Conference (RusAutoCon). IEEE, 2021. P. 421-425, doi: 10.1109/RusAutoCon52004.2021.9537317.

- M.M. Hafizur Rahman, F. Al Faisal, R.M. Nor, T.M.T. Sembok, D.K. Behera, and Y. Inoguchi, “Cost Effectiveness Analysis of a Vertical Midimew-Connected Mesh Network (VMMN),” in Advances in Intelligent Systems and Computing, 2017, pp. 45–53, doi: 10.1007/978-981-10-3874-7_5.

Project leaders

Senior Lecturer

Have you spotted a typo?

Highlight it, click Ctrl+Enter and send us a message. Thank you for your help!

To be used only for spelling or punctuation mistakes.