Unified environment for high-level network modeling on a chip

At present, the use of networks on a chip is a promising approach to organizing a communication subsystem for transmitting data between nodes of computer systems. A single environment for high-level modeling of STNK allows you to optimize and automate the process, which makes the project relevant and interesting.

The development of networks on a chip consists of several successive stages, and high-level modeling is one of them, the subsequent stages of the development of STNC depend on it. At this stage, with the help of models, according to the parameters selected at the design stage, the approximate characteristics of various STNK configurations are evaluated.

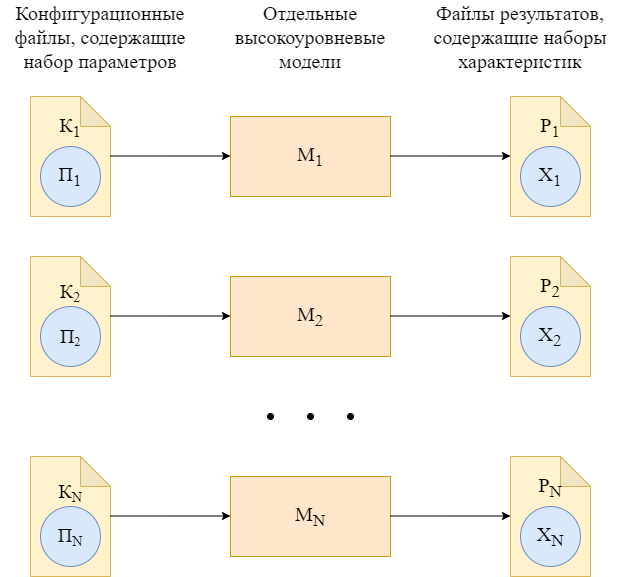

Models:

Each of the models works only with a part of the existing parameters and calculates only a part of the existing characteristics. In addition, there is a possibility of critical errors in the calculation process, which can later have a negative impact on the development of the network on a chip.

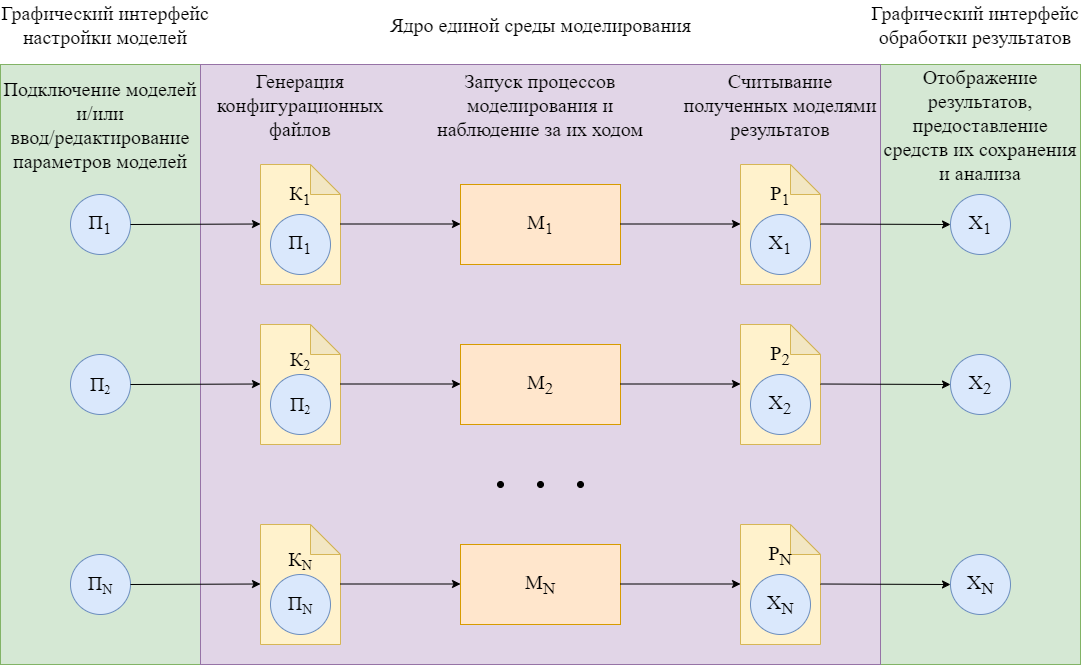

Single environment:

The principle of operation of a single environment, the expansion of which the project is dedicated to, differs from the scheme of operation of the models presented above. The program allows you to connect network models on a chip of various types, which calculate the characteristics of the network according to the entered parameters. Also, a single environment makes it possible to configure the parameters of connected models using a graphical interface.

The integration of models of various types allows you to increase the number of adjustable parameters and measured characteristics. In addition, the probability of errors in the calculation of those characteristics that are calculated by at least two models is reduced, since we are able to compare the results of calculations in such cases. The total simulation time is reduced due to the parallel execution of calculations by simulators. In addition, the environment increases the degree of automation of the modeling process and simplifies it from the point of view of the user researcher.

Objective of the project:

Expanding the capabilities of the integrated environment for high-level modeling of StnK.

Tasks:

- finalization of the internal architecture of the application;

- expanding the capabilities of the graphical interface;

- adaptation and integration of new types of models;

- development and implementation of modeling optimization algorithms.

Stages of project implementation:

The project team:

Borodin Nikolai Yurievich (MKS212) - high-level language programmer

Ponomarev Alexander Sergeevich (MKS211) - leader, high-level language programmer

Rakhmankulova Sabina Erlanovna (BIV204) - trainee

Savastyanova Alexandra Vladimirovna (BIV203) - trainee

Tarzhanov Timofey Vladimirovich (MKS211) - high-level language programmer

Have you spotted a typo?

Highlight it, click Ctrl+Enter and send us a message. Thank you for your help!

To be used only for spelling or punctuation mistakes.